2

4

## **Digital IC Terminology**

- · Current and voltage parameters

- Fan-Out

- · Propagation delays

- · Power requirements

- Noise immunity

- · Invalid voltage levels

- Current-sourcing and current-sinking action

- IC Packages

8/5/2019

CSE, Rajshahi University

#### **Digital IC Terminology**

Dept. of Computer Science and Engineering

University of Rajshahi

**Dr. Shamim Ahmad**

www.ru.ac.bd

- Current and voltage parameters

- Fan-Out

- · Propagation delays

- · Power requirements

- · Noise immunity

- · Invalid voltage levels

- Current-sourcing and current-sinking action

- IC Packages

8/5/2019

CSE, Rajshahi University

3

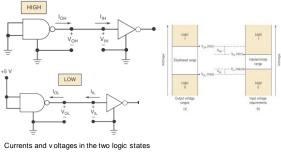

#### **Current and voltage parameters**

CSE, Rajshahi University

8/5/2019

# Current and voltage parameters Voltage Levels

- +  $V_{\text{IH}}(\text{min})$ : High Level Input Voltage : minimum voltage level required for logic 1 at an input

- V<sub>IL</sub>(max): Low Level Input Voltage : maximum voltage level required for logic 0 at an input

- V<sub>oH</sub>(min): High Level Output Voltage : minimum voltage level at an output for logic 1 state

- V<sub>oL</sub>(max): Low Level Output Voltage : maximum voltage level at an output for logic 1 state

#### Current and voltage parameters Current Levels

- $I_{I\!H}$  : High Level Input Current : Current flowing into an input at a logic state 1

- $\textbf{I}_{\textbf{IL}}$  : Low Level Input Current : Current flowing into an input at a logic state 0

- +  $I_{\text{OH}}$  : High Level Output Current : Current flowing from an output at logic state 1

- I<sub>oL</sub>: Low Level Output Current : Current flowing from an output at logic state 0

CSE. Raishahi University

8/5/2019

CSE, Rajshahi University

#### Fan-Out

- Maximum number of logic inputs that an output can drive reliably

- Depends on the logic family

- Example: a logic gate specified with a fan-out of 10, can drive 10 logic inputs. If this is exceeded, the output logic levels cannot be guaranteed

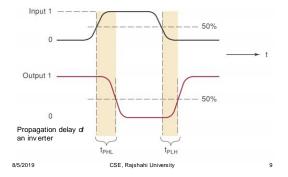

#### **Propagation Delay**

- Delay encountered by a signal in going through a circuit

tPLH delay time in going from logic 0 to logic 1

- $t_{\text{PHL}}$  delay time in going from logic 1 to logic 0

- +  $t_{\text{PLH}}$  and  $t_{\text{PHL}}$  are not necessarily the same values

- Propagation Delay is a measure of the relative speed of logic circuits. The smaller the delay, the faster the circuit

8/5/2019

CSE, Rajshahi University

7

5

8/5/2019

8/5/2019

CSE, Rajshahi University

8

#### **Propagation Delay**

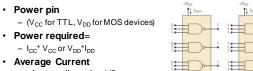

#### **Power Requirements**

- $I_{CC(avg)} = (I_{CCH} + I_{CCL})/2$

- P(avg)= I<sub>CC(avg)</sub> \* V<sub>CC</sub>

8/5/2019

CSE, Rajshahi University

10

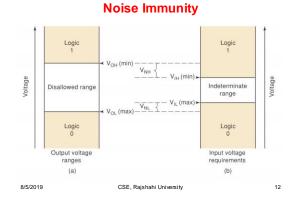

#### **Noise Immunity**

High-state noise margin,

$V_{NH}$ =  $V_{OH}(min) - V_{IH}(min)$ Negative noise spikes greater than  $V_{NH}$  can cause the voltage to drop into the indeterminate range

· Low-state noise margin,

V<sub>NL</sub>= V<sub>IL</sub>(max)- V<sub>OL</sub>(max)

Positive noise spikes greater than  $V_{\text{NL}}$  can cause the voltage to rise into the indeterminate range

## Invalid Voltage Levels

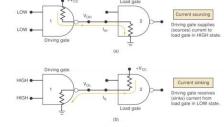

#### **Current-Sourcing and Current-Sinking Action**

- Proper operation requires the input voltages be kept outside the indeterminate range

(less than V<sub>IL</sub>(max) or greater than V<sub>IH</sub>(min)

- Voltage output (connected to an input) could be outside the valid region due to malfunctioning or being overloaded (fan-out exceeded)

- Power supply voltages outside acceptable range can cause invalid voltage levels.

8/5/2019

An output must be able to source or sink a current when connected to an input

CSE, Rajshahi University 13 8/5/2019 CSE, Rajshahi University

The TTL Logic Family

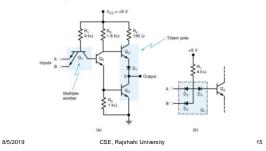

• The NAND gate is a basic TTL circuit.

#### The TTL Logic Family

- Current sinking action: A TTL output acts as a current sink in the low state

- Current sourcing action: A TTL output acts as a current source in the high state

8/5/2019

CSE, Rajshahi University

16

## The TTL Logic Family

- · TTL circuits have a similar structure

- The input will be the cathode of a PN junction

- A HIGH input will turn off the junction and only a leakage current is generated.

- A LOW input turns on the junction and a relatively large current is generated

- Most TTL circuits have some type of totem-pole

output configuration

CSE. Raishahi University

#### **TTL Data Sheets**

- First line of TTL ICs was the **54/74** series - 54 series operates over a wider temperature range

- Same numbering system, **prefix** indicates manufacturer

- SN Texas Instruments

- DM National Semiconductor

- S Signetics

8/5/2019

- DM7402, SN7402, S7402 all perform the same function

- Data sheets contain electrical characteristics, switching characteristics, and recommended operating conditions.

CSE, Rajshahi University

17

#### **TTL Data Sheets**

#### recommended operating conditions

|     |                                | SN  | SN54ALS00A |      | SN74ALS00A |       |     | UNIT |  |

|-----|--------------------------------|-----|------------|------|------------|-------|-----|------|--|

|     | - A (C)                        | MIN | NOM        | MAX  | MIN        | NOM   | MAX | UNIT |  |

| Vcc | Supply voltage                 | 4.5 | 5          | 5.5  | 4.5        | 5     | 5.5 | V    |  |

| VIH | High-level input voltage       | 2   |            |      | 2          |       |     | V    |  |

| VIL | Low-level input voltage        |     |            | 0.8‡ |            |       | 0.8 | v    |  |

| VIL | VIL Low-level input voltage    |     |            | 0.7§ |            |       |     |      |  |

| ЮН  | High-level output current      |     | -0.4       |      |            | -0.4  |     |      |  |

| IOL | Low-level output current       |     |            | 4    |            | -1301 | 8   | mA   |  |

| TA  | Operating free-air temperature | -55 |            | 125  | 0          |       | 70  | C    |  |

<sup>‡</sup> Applies over temperature range – 55°C to 70°C § Applies over temperature range 70°C to 125°C

#### 8/5/2019

8/5/2019

CSE, Rajshahi University

19

Vcc = 4.5 V

V<sub>CC</sub> = 5.5 V<sub>CC</sub> = 5.5

VCC = 5.5

Vcc = 5.5

PARAMETER

VIK VOH

1н 11 10<sup>‡</sup>

ICCH

8/5/2019

CSE, Rajshahi University

e a current that closely appro

**TTL Data Sheets**

electrical characteristics over recommended operating free-air temperature range unless otherwise noted)

TYPT

TEST CONDITIONS

V<sub>I</sub> = 7 V V<sub>I</sub> = 2.7 V

VI = 0.4 V VO = 2.25 UNIT

ν

MIN TYPT

nates one half of the true short-circuit output ci

## **TTL Data Sheets**

| switching | characteristics | (see | Figure | 1) |

|-----------|-----------------|------|--------|----|

| PARAMETER        | FROM   | TO<br>(OUTPUT) | CL    | C = 4.5 V to 5.5 V,<br>= 50 pF,<br>= 500 Ω,<br>= MIN to MAX§ |     |            | UNIT |

|------------------|--------|----------------|-------|--------------------------------------------------------------|-----|------------|------|

|                  |        |                | SN54A | SN54ALS00A                                                   |     | SN74ALS00A |      |

|                  |        | 1              | MIN   | MAX                                                          | MIN | MAX        |      |

| <sup>1</sup> PLH | A or B |                | 3     | 15                                                           | 3   | 11         |      |

| 1PHL             | A OF B | r              | 2     | 9                                                            | 2   | 8          | ns   |

#### **TTL Series Characteristics**

- Standard 74 series TTL has evolved into other series:

- Standard TTL, 74 series

- Schottky TTL, 74S series

- Low power Schottky TTL, 74LS series (LS-TTL)

- Advanced Schottky TTL, 74AS series (AS-TTL)

- Advanced low power Schottky TTL, 74ALS series

- 74F fast TTL

8/5/2019

| 8/5 | /201 | a |

|-----|------|---|

|     |      |   |

CSE, Rajshahi University

21

CSE, Rajshahi University

22

## **TTL Series Characteristics**

|                          | 74  | 745 | 74LS    | 74AS | 74ALS    | 74F |

|--------------------------|-----|-----|---------|------|----------|-----|

| Performance ratings      |     |     | and the | -    | 11-11-10 | 1   |

| Propagation delay (ns)   | 9   | 3   | 9.5     | 1.7  | 4        | 3   |

| Power dissipation (mW)   | 10  | 20  | 2       | 8    | 1.2      | 6   |

| Speed-power product (pJ) | 90  | 60  | 19      | 13.6 | 4.8      | 18  |

| Max. clock rate (MHz)    | 35  | 125 | 45      | 200  | 70       | 100 |

| Fan-out (same series)    | 10  | 20  | 20      | 40   | 20       | 33  |

| Voltage parameters       |     |     |         |      |          |     |

| V <sub>OH</sub> (min)    | 2.4 | 2.7 | 2.7     | 2.5  | 2.5      | 2.5 |

| V <sub>OL</sub> (max)    | 0.4 | 0.5 | 0.5     | 0.5  | 0.5      | 0.5 |

| V <sub>IH</sub> (min)    | 2.0 | 2.0 | 2.0     | 2.0  | 2.0      | 2.0 |

| V <sub>II</sub> (max)    | 0.8 | 0.8 | 0.8     | 0.8  | 0.8      | 0.8 |

8/5/2019

CSE, Rajshahi University

23

## **TTL Loading and Fan Out**

- Fan out refers to the load drive capability of an IC output

- A TTL output has a limit on how much current it can sink in the LOW state

- A TTL output has a **limit on how** much current it **can** source in the HIGH state.

- Exceeding these currents will result in output voltage levels outside specified ranges

8/5/2019

## **TTL Loading and Fan Out**

- · Determining fan out

- Add the I<sub>H</sub> for all inputs connected to an output. The sum must be less than the output  $I_{OH}$  specification.

- Add the  $I_{\rm L}$  for all inputs connected to an output. The sum must be less than the output  $I_{OL}$  specification.

- See example 8-5 page 510

#### **TTL Loading and Fan Out**

· Determining fan out :

8/5/2019

How many 74ALS00 NAND gate inputs can be driven by a 74ALS00 NAND gate output?

IoL(max)=8 mA IIL(max)=0.1 mA fan-out (low)= I<sub>oL</sub>(max)/ I<sub>IL</sub>(max)=8/0.1=80 I<sub>oH</sub>(max)=0.4 mA=400μA I<sub>IH</sub>(max)=20μA fan-out (high)= I<sub>oH</sub>(max)/ I<sub>IH</sub>(max)=400/20=20

Choose the smaller:Fan-out=20

Therefore, the 74ALS00 NAND gate can drive up to 20 other 74ALS00 NAND gates

8/5/2019

CSE. Raishahi University

25

CSE. Raishahi University

26

## Other TTL Characteristics

- Unconnected (floating) inputs: an input unconnected acts like a logic 1 applied to that input. left

- Unused inputs: (will pick noise)

- Tied together inputs : Input current = sum of individual currents single current for NAND/AND gates in low states

#### Current transients

- When a totem pole TTL output goes from LOW to HIGH, a high amplitude current spike is drawn from the  $V_{\rm CC}$  supply Ceramic disk capacitors (.01 or .1  $\mu F)$  are used to short these high frequency spikes to ground.

27

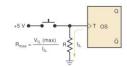

#### **Other TTL Characteristics**

· Biasing TTL inputs Low R is needed to keep the T input low while the switch is open

Voltage drop across R should be less than VIL (max)  $R_{max} = (V_{IL}(max)/I_{IL})$

R is chosen slightly below R<sub>max</sub> to reduce current drain Example: (V<sub>IL</sub>(max) = 0.8 V I<sub>IL</sub> = 0.4 mA

$R_{max} = 0.8 V/0.4 m A = 2000 \Omega$ Choose R=1.8kΩ (standard resistor)

8/5/2019

## **MOS Technology**

- Metal Oxide Semiconductor Field Effect Transistors (MOSFETs)

- Simple and cheap to fabricate

- Consume very little power

8/5/2019

- More circuit elements are possible

- Susceptible to static electricity damage

CSE, Rajshahi University

29

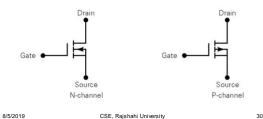

#### MOS Technology

• Schematic symbols for P and N channel enhancement MOSFETs.

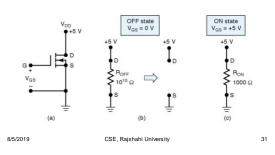

**MOS Technology**

· The basic MOSFET switch

#### **Complementary MOS Logic**

- P-MOS uses only P channel enhancement MOSFETs

- N-MOS uses only N channel enhancement MOSFETs

- CMOS uses both P and N channel devices

- Faster

- Consumes less power

- More complex fabrication

8/5/2019

CSE, Rajshahi University

## **Complementary MOS Logic**

|                       | CMOS  |      |       |      |       |       |        |     | TTL  |      |

|-----------------------|-------|------|-------|------|-------|-------|--------|-----|------|------|

| Parameter             | 4000B | 74HC | 74HCT | 74AC | 74ACT | 74AHC | 74AHCT | 74  | 74LS | 74A5 |

| V <sub>IH</sub> (min) | 3.5   | 3.5  | 2.0   | 3.5  | 2.0   | 3.85  | 2.0    | 2.0 | 2.0  | 2.0  |

| V <sub>IL</sub> (max) | 1.5   | 1.0  | 0.8   | 1.5  | 0.8   | 1.65  | 0.8    | 0.8 | 0.8  | 0.8  |

| V <sub>OH</sub> (min) | 4.95  | 4.9  | 4.9   | 4.9  | 4.9   | 4.4   | 3.15   | 2.4 | 2.7  | 2.7  |

| V <sub>OL</sub> (max) | 0.05  | 0.1  | 0.1   | 0.1  | 0.1   | 0.44  | 0.1    | 0.4 | 0.5  | 0.5  |

| VNH                   | 1.45  | 1.4  | 2.9   | 1.4  | 2.9   | 0.55  | 1.15   | 0.4 | 0.7  | 0.7  |

| VNL                   | 1.45  | 0.9  | 0.7   | 1.4  | 0.7   | 1.21  | 0.7    | 0.4 | 0.3  | 0.3  |

| 8/5/2019 |  |

|----------|--|

CSE, Rajshahi University

33

#### **CMOS Series Characteristics**

- CMOS devices compete directly with TTL

Pin compatible

- Functionally equivalent

- Electrically compatible

- 4000/1400 series

- +000/1+00 36

- 74C series

- 74HC/HCT (high-speed CMOS) are functionally and pin compatible with TTL IC's with the same name. The HCT is also electrically compatible with TTL

CSE, Rajshahi University

8/5/2019

34

#### **CMOS Series Characteristics**

- 74AC/ACT (advanced CMOS)

- 74AHC/AHCT (advanced high-speed CMOS)

- · BiCMOS 5-volt logic

| CMOS | Series | Characteristics |

|------|--------|-----------------|

|------|--------|-----------------|

- +  $\mathbf{P}_{\mathbf{D}}$  increases with frequency

- Fan out (large)

- Switching speed

- Unused inputs (will pick static, cause heat, invalid output). Unused inputs should be connectd to 0V or  $V_{\text{DD}}$  or another input

- Static sensitivity – ESD precautions

- ESD piecauli

- Latch up

8/5/2019

35

8/5/2019

CSE, Rajshahi University

#### Low Voltage Technology

#### · CMOS family:

- 74LVC (low voltage CMOS)

- 74ALVC (advanced low voltage CMOS)

- 74LV (low voltage)

- 74AVC (advanced very low voltage CMOS)

- 74AUC (advanced ultra-low voltage CMOS)

- 74AUP (advanced ultra-low power)

- 74CBT (cross bartechnology)

- 74CBTLV (cross bar technology low voltage)

- 74GTLP (gunning transceiver logic plus)

- 74SSTV (stub series terminated logic)

- 74TVC (translation voltage clamp)

8/5/2019

CSE, Rajshahi University

37

#### Low Voltage Technology

BiCMOS family:

8/5/2019

- 74LVT (low voltage BiCMOS technology)

- 74ALVT (advanced low voltage BiCMOS technology)

- 74ALB (advanced low voltage BiCMOS)

- 74VME (VERSA Module Eurocard)

- The move toward low voltage systems will continue and the technician must be prepared to operate in an environment where devices may not necessarily operate on 5 volts.

CSE. Raishahi University

Open Collector/Open Drain Outputs

- Conventional CMOS outputs and TTL totem pole outputs should never be connected to the same point. (will fight each other)

- Open-collector/open-drain outputs (need an external pull-up resistor to V<sub>CC</sub>. (the pull-up transistor of the totem pole is removed)

- Open-collector/open-drain buffer/drivers

- · IEEE/A NSI symbols for open collector/drain outputs

CSE, Rajshahi University

8/5/2019

39

#### Tristate (Three-State) Logic Outputs

- Three states are possible: HIGH, LOW, and high impedance.

- · Advantages of tristate devices

- Tristate buffers

- Tristate ICs

- · IEEE/ANSI symbol for tristate outputs

8/5/2019

40

#### · Basic ECL circuit · At high frequencies bus wires of more than about 4 · ECL OR/NOR gate inches in length act like transmission lines. · ECL characteristics · In order to prevent reflected waves, the end of a bus must be terminated with a resistance equal to the line - -0.8 V logic 1, -1.7 V logic 0 impedance (about 50 Ohms). - Noise margins approximately 150 mV - Output complement is produced, eliminating need for · Figure 8-40 illustrates termination techniques. inverters - Typical fan out is 25

## The ECL Digital IC Family

- Emitter coupled logic increases switching speed.

- Very fast switching, typical propagation delay is 360 ps

- Typical power dissipation is 25 mW

- Current flow remains constant, eliminating noise spikes

8/5/2019

CSE. Raishahi University

**High-Speed Bus Interface Logic**

41

8/5/2019

CSE. Raishahi University

42

44

#### **CMOS Transmission Gate** (Bilateral Switch)

- · Acts as a single pole, single throw switch

- · Controlled by an input logic level

- · Passes signals in both directions

- · Signals applied to the input can be analog or digital

- Input must be between 0 and V<sub>DD</sub> volts.

## **IC** Interfacing

- Driver provides the output signal.

- · Load receives the signal.

- · Interface circuit connected between driver and load to condition the signal for the load.

- Interfacing between logic families is common in digital systems.

8/5/2019

CSE, Rajshahi University

43

8/5/2019

CSE, Rajshahi University

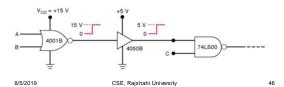

#### Interfacing 5-V TTL and CMOS

- TTL easily meets CMOS input current requirements. CMOS can drive TTL loads.

- TTL output voltage must be raised for input to some CMOS devices. The most common solution is a pull-up resistor.

CSE. Raishahi University

#### Interfacing 5-V TTL and CMOS

- · CMOS output for both logic states

- · CMOS driving TTL in the HIGH state

- CMOS driving TTL in the LOW state

- High voltage CMOS driving TTL

#### Analog Voltage Comparators

- · Useful in systems with analog and digital components

- Compares two voltages. If voltage on the (+) input is greater than (-) input the output is high. If input on the (-) is greater the output is low.

- May be considered a one bit analog to digital converter.

- •

8/5/2019

## Troubleshooting

- Logic pulser tool that generates a short pulse when actuated

- Senses the existing voltage level and produces a pulse in the opposite polarity

- Output impedance of 2 Ohms or less

- · Using logic pulser and probe to test a circuit

- · Finding shorted nodes

| 8/5/2019 |

|----------|

|----------|

CSE, Rajshahi University

47

45

8/5/2019

CSE, Rajshahi University