PAL and PLA

Dept. of Computer Science and Engineering University of Rajshahi www.ru.ac.bd

**Dr. Shamim Ahmad**

- Programmable Array Logic (PAL)

- Monolithic Memories, Inc. (MMI)

- March 1978

- Registered trademark on the term PAL

- "Programmable Semiconductor Logic Circuits".

- The trademark

- Currently held by Lattice Semiconductor

- Signetics

- Field programmable logic array (FPLA)

- **1**975

- Unfamiliar to most circuit designers

- Perceived to be too difficult to use

- Slow maximum operating

- Large package, a 600-mil (0.6", or 15.24 mm) wide 28-pin

PAL devices consisted of a small PROM

- One-time programmable

- Hard array logic

•

- mask-programmed at the factory

- UV erasable versions

- PALCxxxxx, Example PALC22V10

PAL devices consisted of a small PROM

- Flash erasable devices

- PALCExxx, Example: PALCE22V10

- Electrically-erasable

- GAL : Generic array logic, gate array logic

- Lattice Semiconductor

- AMD

- National Semiconductor

- GAL22V10

## **Bipolar transistor technology**

- Early PALs were 20-pin DIP components

- One-time programmable (OTP) titanium-tungsten programming

- Lattice Semiconductor

## CMOS Technology.

- Cypress

- Lattice Semiconductor

- Advanced Micro Devices (AMD)

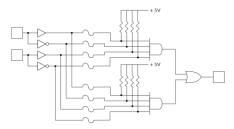

Simplified programmable logic device

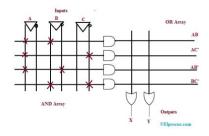

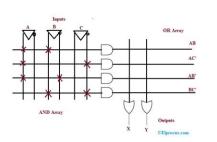

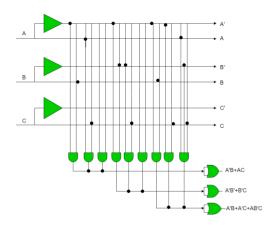

True and complemented inputs to the AND gates.

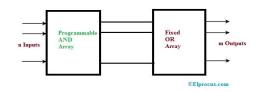

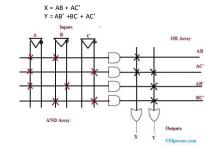

**"Fixed-OR, Programmable-AND"** AND gates -> product terms, OR gates -> sum-of-products logic array.

#### Programmable logic plane

- The programmable logic plane is a programmable read-only memory

- That allows the signals present on the device pins

- The logical complements of those signals

- To be routed to output logic ro macrocells

- Output logic

- The early 20-pin PALs had 10 inputs and 8 outputs.

- The outputs were active lowRegistered

- Combinational.

3

| u o laef   |                                       | HESET .          |

|------------|---------------------------------------|------------------|

|            |                                       |                  |

|            |                                       |                  |

|            |                                       |                  |

| 10-00      | BLE                                   |                  |

| 0-2-       | MMA<br>RRA<br>X44)                    |                  |

|            | PROGRAMMABLE<br>AND-ARRAY<br>(132X44) |                  |

|            | PRO                                   | IS OUNCE IN NOVO |

| 10-00      |                                       |                  |

| 10-0-      |                                       |                  |

| 10-02-02-0 |                                       |                  |

|            |                                       |                  |

101

- PAL16L8

- 8 combinational outputs

- PAL16R8

- 8 registered outputs

- PAL16R6

- 6 registered and 2 combinationalPAL16R4

- 4 registered and 4 combinational

8/5/2019

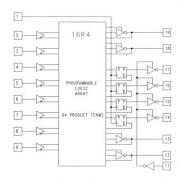

#### 22V10

- 24 pin device with 10 output logic macrocells

- Each macrocell

- Combinational

- Registered

- Active high

- Active low.

- The number of product terms allocated to an output varied from 8 to 16

- PAL16V8, PAL20V8

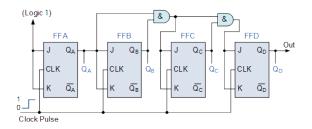

# The PALASM (from "PAL assembler")

| PAL16 |    | PAL  |   |      |     | PAI  |     | ESIC | IN SP | ECIF | ICATIO |

|-------|----|------|---|------|-----|------|-----|------|-------|------|--------|

| 4 bit |    | unte |   | witt |     | nch  | ror | ous  | clea  | r    |        |

| Micha |    |      |   |      |     |      |     |      |       |      |        |

| Clk   |    |      |   |      |     |      |     |      |       | NC   | GND    |

|       |    |      |   |      |     |      |     |      | NC    |      | VCC    |

| Q3    |    | Cle  |   |      |     |      |     |      |       |      |        |

|       |    | /03  |   |      | * / | Q1 1 | • / | 00   |       |      |        |

|       |    | Q3   |   |      |     |      |     |      |       |      |        |

|       |    | Q3   |   |      |     |      |     |      |       |      |        |

|       | +  | Q3   | ٠ | Q2   |     |      |     |      |       |      |        |

| Q2    |    | C14  |   |      |     |      |     |      |       |      |        |

|       |    | /02  |   |      | * / | Q0   |     |      |       |      |        |

|       |    | Q2   |   |      |     |      |     |      |       |      |        |

|       | +  | 02   | ٠ | Q1   |     |      |     |      |       |      |        |

| Q1    |    | Cl   |   |      |     |      |     |      |       |      |        |

|       |    | /01  |   |      |     |      |     |      |       |      |        |

|       | +  | 01   | • | 00   |     |      |     |      |       |      |        |

| Q0    |    | Cl   |   |      |     |      |     |      |       |      |        |

|       | +  | /00  |   |      |     |      |     |      |       |      |        |

| FUNC  |    |      |   |      |     |      |     |      |       |      |        |

| OEC   |    |      |   |      |     |      |     |      |       |      |        |

|       | н  | c    |   |      | I   |      | L   |      |       |      |        |

| τ.    | τ. | C    |   |      |     |      |     |      |       |      |        |

| L     | L  | C    |   | 1    |     |      | τ.  | T.   |       |      |        |

| L     | L  | c    |   | н    |     | 18   | L   | L    |       |      |        |

| L     | L  | c    |   | L    | 1   |      | н   | L    |       |      |        |

|       | н  | c    |   | L    |     |      |     | L    |       |      |        |

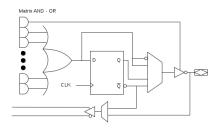

# The programmable logic device (PLD)

- One kind of chip

- Used to implement the logic circuit

- It includes a set of logic circuit elements

- That can be modified in several ways.

- PLDs (different types)

- SPLD-simple PLD (PLA & PAL)

- CPLD-complex PLD

- FPGAs-field programmable gate arrays.

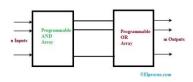

Programmable Array Logic

Programmable Logic Array

Design of Programmable Array Logic (PAL)

X =AB +AC' ??? Y= AB'+B' ???

Design of Programmable Logic Array (PLA)

8/5/2019

- Field-Programmable Gate Array" or FPGA.

- Intel (who acquired Altera)

- Xilinx