### **Counters Based on Shift Register**

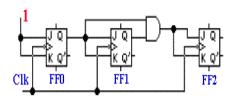

- The output of LSB FF is connected as D input to MSB FF.

- This is commonly called as Ring Counter or Circular Counter. The data is shifted to right with each clock pulse. This counter has four different states. This can be extended to any no. of bits.

Dept. of Computer Science and Engineering University of Rajshahi www.ru.ac.bd

**Dr. Shamim Ahmad**

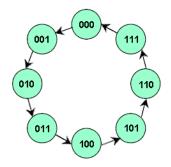

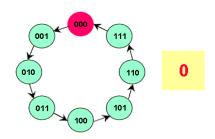

#### Twisted Ring Counter or Johnson Counter **Mod-8 Johnson Counter**

The complement output of LSB FF is connected as D input to MSB FF.

- This is commonly called as Johnson Counter. The data is shifted to right with each clock pulse. This counter has eight different states. This can be extended to any no. of bits.

Mod-7 Twisted Ring Counter

□ The D input to MSB FF is

- D The counter follows seven different states with application of clock input.

- □ By changing feedback different counters can be obtained.

# **Design Procedure for Synchronous Counter**

- □ The clock input is common to all Flip-Flops.

- Any Flip-Flop can be used.

- For mod-n counter 0 to n-1 are counter states.

The excitation table is written considering the

- present state and next state of counter.The flip-flop inputs are obtained from characteristic equation.

- By using flip-flops and logic gate the implementation of synchronous counter is obtained.

#### Difference between Asynchronous and Synchronous Counter

| Asynchronous Counter             | Synchronous Counter               |  |  |

|----------------------------------|-----------------------------------|--|--|

| 1. Clock input is applied to LSB | 1. Clock input is common to all   |  |  |

| FF. The output of first FF is    | FF.                               |  |  |

| connected as clock to next FF.   |                                   |  |  |

| 2. All Flip-Flops are toggle FF. | 2. Any FF can be used.            |  |  |

| 3. Speed depends on no. of FF    | 3. Speed is independent of no. of |  |  |

| used for n bit.                  | FF used.                          |  |  |

| 4. No extra Logic Gates are      | 4. Logic Gates are required based |  |  |

| required. Cost is less.          | on design. Cost is more.          |  |  |

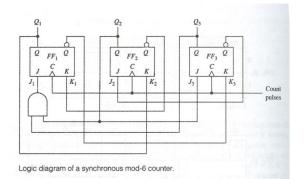

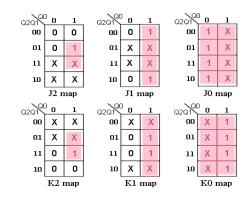

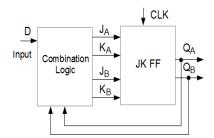

# Design of Mod-6 Synchronous counter

- The count sequence for Mod-6 counter is as follows:

- 000,010,011,110,101,001

- Excitation table is formed for given count sequence.

- Flip-flop inputs are derived from present state and next state.

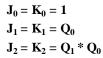

- From K –map simplification the Flip-flop input equations are obtained.

- Logic diagram of Mod-6 counter is drawn by using JK-FF and logic gates.

Excitation table for a synchronous mod-6 counter using clocked JK flip-flops

| Present state |    |       | Next state |         | Flip-flop inputs |       |                |       |                |       |                |

|---------------|----|-------|------------|---------|------------------|-------|----------------|-------|----------------|-------|----------------|

| $Q_1$         | Q2 | $Q_3$ | $Q_1^+$    | $Q_1^+$ | $Q_3^+$          | $J_1$ | K <sub>1</sub> | $J_2$ | K <sub>2</sub> | $J_3$ | K <sub>3</sub> |

| 0             | 0  | 0     | 0          | 1       | 0                | 0     | -              | 1     | -              | 0     | -              |

| 0             | 1  | 0     | 0          | 1       | 1                | 0     | -              | -     | 0              | 1     | -              |

| 0             | 1  | 1     | 1          | 1       | 0                | 1     | -              | -     | 0              | -     | 1              |

| 1             | 1  | 0     | 1          | 0       | 1                | -     | 0              | -     | 1              | 1     | -              |

| 1             | 0  | 1     | 0          | 0       | 1                | -     | 1              | 0     | -              | -     | 0              |

| 0             | 0  | 1     | 0          | 0       | 0                | 0     | -              | 0     | -              | -     | 1              |

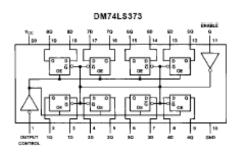

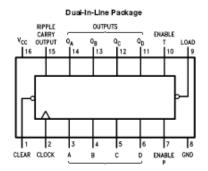

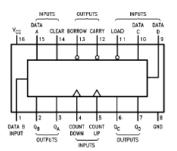

# DM54161/DM74161/DM74163 Synchronous 4-Bit Counters

DM74LS193 Synchronous 4-Bit Binary Counter with Dual Clock

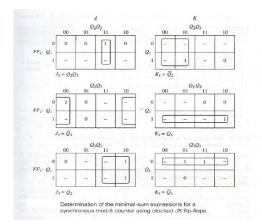

This example is taken from T. L. Floyd, *Digital Fundamentals*, Fourth Edition, Macmillan Publishing, 1990, p.395.

| Present State | Next State    |

|---------------|---------------|

| $Q_2 Q_1 Q_0$ | $Q_2 Q_1 Q_0$ |

| 0 0 0         | 0 0 1         |

| 0 0 1         | 0 1 0         |

| 0 1 0         | 0 1 1         |

| 0 1 1         | 1 0 0         |

| 1 0 0         | 1 0 1         |

| 1 0 1         | 1 1 0         |

| 1 1 0         | 1 1 1         |

| 1 1 1         | 0 0 0         |

CIk\_

| Output State                                                  | Fl                                                         | Flip-flop inputs |                           |     |  |

|---------------------------------------------------------------|------------------------------------------------------------|------------------|---------------------------|-----|--|

| Present State<br>Q <sub>2</sub> Q <sub>1</sub> Q <sub>0</sub> | Next State<br>Q <sub>2</sub> Q <sub>1</sub> Q <sub>0</sub> | J2 K2            | $J_2 K_2 = J_1 K_1 = J_1$ |     |  |

| 000                                                           | 0 0 1                                                      | 0 X              | 0 X                       | 1 X |  |

| 0 0 1                                                         | 0 1 0                                                      | 0 X              | 1 X                       | X 1 |  |

| 0 1 0                                                         | 0 1 1                                                      | 0 X              | X 0                       | 1 X |  |

| 0 1 1                                                         | 1 0 0                                                      | 1 X              | X 1                       | X 1 |  |

| 100                                                           | 1 0 1                                                      | X 0              | 0 X                       | 1 X |  |

| 101                                                           | 1 1 0                                                      | X 0              | 1 X                       | X 1 |  |

| 1 1 0                                                         | 1 1 1                                                      | X 0              | X 0                       | 1 X |  |

| 111                                                           | 0 0 0                                                      | X 1              | X 1                       | X 1 |  |

8/5/2019