|                                                 | Doping                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Doping & Ion Implantation<br>Cahpter-11 of Text | Doping is a process where a specific elements<br>is introduced into intrinsic semiconductor<br>materials to increase its conductivity. The<br>doped material displays two unique properties<br>that are the basis of solid-state electronics.<br>The two properties are<br>1. Precise resistivity control through doping<br>2. Electron ( <i>N-type</i> ) and hole ( <i>p-type</i> ) conduction |

1

#### Junction

A junction is the separation between a region that is rich in negative electrons (N-type region) and a region that is rich in holes (P-type region). The exact location of a junction is where the concentration of electrons equals the concentration of holes. The usual way to form junctions in the surface of semiconductor wafer is by

> » thermal diffusion » ion implantation

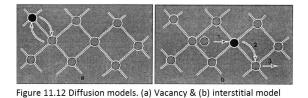

#### Diffusion

Two conditions are necessary for a diffusion to take place

- higher concentration

- sufficient energy

The goals of solid-state:

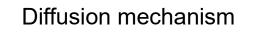

- 1. The creation of a specific number (concentration) of dopant atoms in the wafer surface

- 2. To create an N-P (or P-N) junction at a specific distance below the wafer surface

- 3. To create a specific distribution and concentration of dopant atoms in the wafer surface

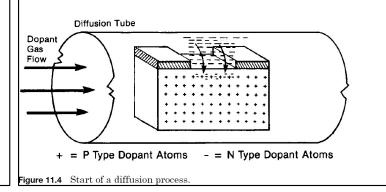

# **Doped Region by Diffusion**

After patterning a hole in the oxide layer, the wafer is exposed to dopant at high temp in a diffusion tube.

| •                         |                                                                                                                 |                                       | unts<br>tivity                |                      | d level<br>e  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------|----------------------|---------------|

|                           |                                                                                                                 |                                       | <u></u>                       |                      | 4             |

| gure 11.5                 | Cross se<br># N's                                                                                               | ection of s                           | wafer at co<br><b>Net</b>     | nclusion             | of diffusion. |

| gure 11.5                 | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - | 22.20                                 |                               | onclusion<br>Layer   | of diffusion. |

|                           | # N's                                                                                                           | # P's                                 | Net                           |                      | of diffusion. |

|                           | # N's<br>(-)                                                                                                    | # P's<br>(+)                          | Net<br>(N - P)                | Layer                | of diffusion. |

| Layer<br>1                | <b># N's</b><br>(-)<br>12                                                                                       | <b># P's</b><br>(+)<br>5<br>5         | Net<br>(N - P)<br>7           | Layer<br>N           | of diffusion. |

| Layer<br>1<br>2<br>3<br>4 | <b># N's</b><br>(-)<br>12<br>10<br>8<br>5                                                                       | # P's<br>(+)<br>5<br>5<br>5<br>5<br>5 | Net<br>(N - P)<br>7<br>5      | Layer<br>N<br>N      | of diffusion. |

| Layer<br>1<br>2<br>3      | <b># N's</b><br>(-)<br>12<br>10<br>8                                                                            | <b># P's</b><br>(+)<br>5<br>5         | Net<br>(N - P)<br>7<br>5<br>3 | Layer<br>N<br>N<br>N | of diffusion. |

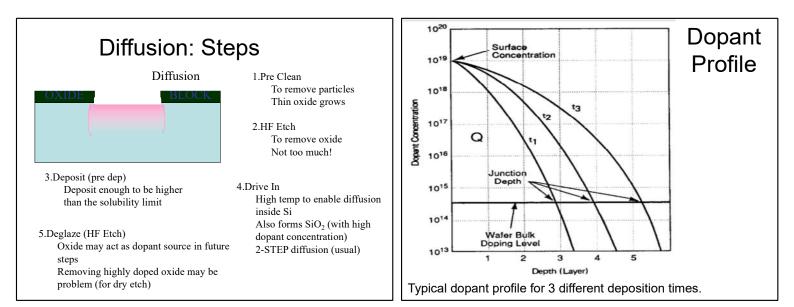

### **Diffusion Process Steps**

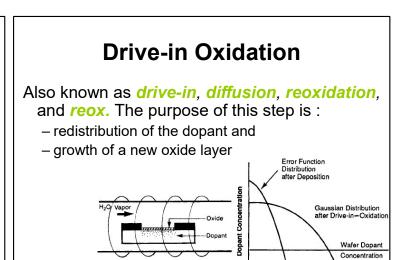

The use of solid-state *thermal diffusion* to create junctions in semiconductor wafers requires two steps.

- deposition, and

- drive-in oxidation.

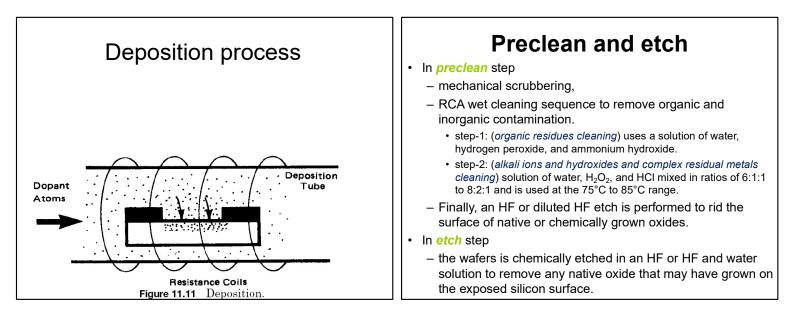

#### Deposition

The first step of a diffusion process is called *deposition*; it is also called *predeposition*, *dep*, or *predep*.

A deposition process is controlled or limited by *two* factors

- Diffusivity, the rate (speed) of movement of the dopant through the particular wafer material

- maximum solid solubility, the max. concentration of a specific dopant that can be put into the wafer

## **Deposition steps**

A deposition process requires four steps.

- 1. Preclean and etch

- 2. Tube deposition

- 3. Deglaze

- 4. Evaluation

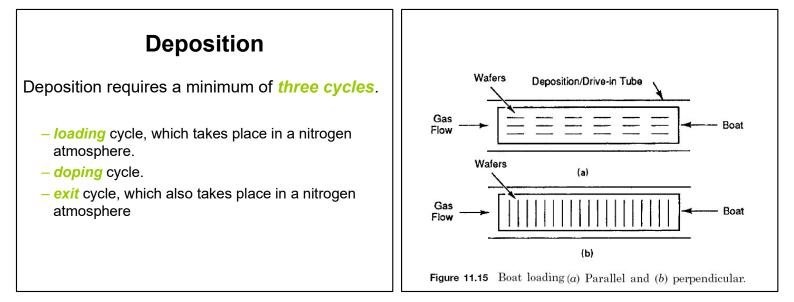

# Perpendicular Vs Parallel placement of wafers in diffusion tube

- Perpendicular (right-angle to the tube axis) placement is the highest packing density, but it can cause uniformity problems, because the wafers act as baffles to the gas flow.

- Parallel placement offers the advantage of more uniform doping, since the doping gas proceeds unimpeded through the wafer boat.

### Deglaze

During the deposition cycle, the formed native oxide gets doped and later can act as an unwanted source of dopant during the drive-in-oxidation step.

- Deposition created oxide can be difficult to etch, causing incomplete etch in a subsequent masking process.

- The term *deglaze* is used to cover the removal of any silicon oxide, diffusion (phosphorus and boron) glass, or nitride coating

- The oxide is removed from the surface by immersion in a diluted HF solution, followed by a water rinse and a drying step.

#### Evaluation

- · Sheet resistance

- C-V measurement to see the surface contaminations

- UV light to see the dirt

Figure 11.22 Drive-in oxidation. (a) Cross section of wafer and (b) dopant concentration in wafer.

Depth Into Wafer

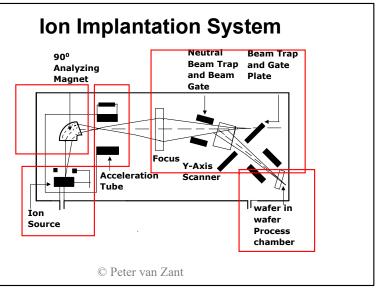

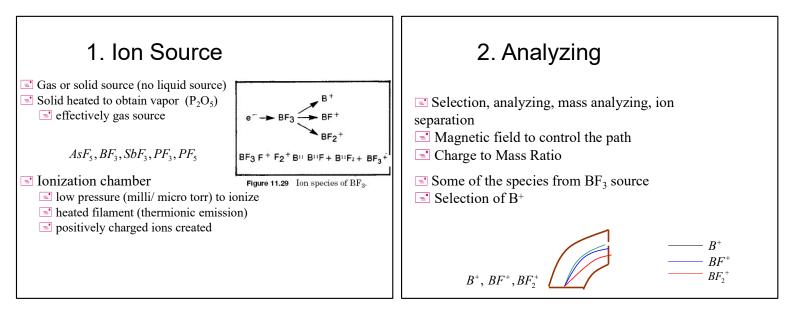

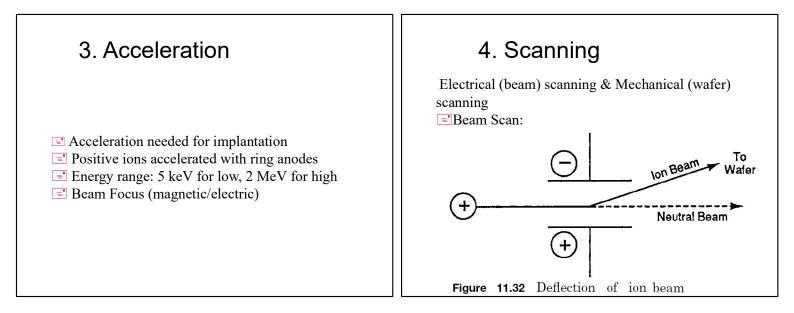

| Ion Implantation                                                                                                                                                                                                                                                                                                                                                                               | Ion Implantation                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Thermal diffusion places a limit on the production of advanced circuits because of <ul> <li>lateral diffusion,</li> <li>ultra thin junctions,</li> <li>poor doping control,</li> <li>surface contamination interference, and</li> <li>dislocation generation.</li> </ul> </li> <li>Ion implantation overcomes these limits of diffusion and also adds additional benefits.</li> </ul> | <ul> <li>No side diffusion,</li> <li>~ room temperature process,</li> <li>Dopant goes inside the silicon</li> <li>Controlled doping <ul> <li>concentration</li> <li>profile (depth)</li> </ul> </li> </ul> |

Ion implantation is a physical process while Diffusion is a chemical process. The dopant atoms physically bombard the wafer, enter the surface, and come to rest below the surface