#### Power consumption analysis

- Almost all power consumption comes from switching behavior.

- Static power dissipation comes from leakage currents.

- Surprising result: power consumption is independent of the sizes of the pullups and pulldowns.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

## Power consumption circuit

■ Input is square wave.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

## Power consumption

- A single cycle requires one charge and one discharge of capacitor:  $E = C_L(V_{DD} V_{SS})^2$ .

- Clock frequency f = 1/t.

- Energy  $E = C_L(V_{DD} V_{SS})^2$ .

- Power = E x f = f  $C_L(V_{DD} V_{SS})^2$ .

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wol

# Observations on power consumption

- Resistance of pullup/pulldown drops out of energy calculation.

- Power consumption depends on operating frequency.

- Slower-running circuits use less power (but not less energy to perform the same computation).

Modern VLSI Design 4e: Chapter

Copyright © 2008 Wayne Wolf

# Speed-power product

- Also known as power-delay product.

- Helps measure quality of a logic family.

- For static CMOS:

- $-SP = P/f = CV^2.$

- Static CMOS speed-power product is independent of operating frequency.

- Voltage scaling depends on this fact.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

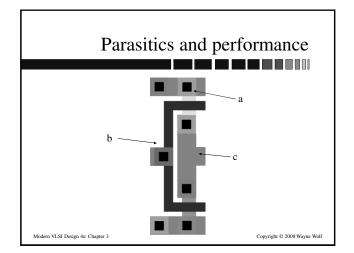

## Effect of parasitics

a: Capacitance on power supply is not bad, can be good in absence of inductance.

Resistance slows down static gates, may cause pseudo-nMOS circuits to fail.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

## Effects of parasitics, cont'd

- b: Increasing capacitance/resistance reduces input slope.

- c: Similar to parasitics at b, but resistance near source is more damaging, since it must charge more capacitance.

$$\begin{array}{c|c} x & & & & & & & & \\ & & & & & & & & \\ & & & & & & & \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & \\ & & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ &$$

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

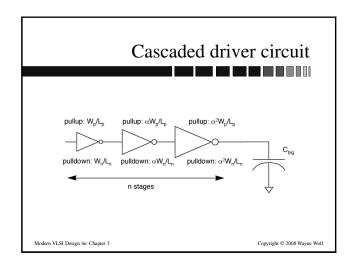

## Driving large loads

- Sometimes, large loads must be driven:

- off-chip;

- long wires on-chip.

- Sizing up the driver transistors only pushes back the problem—driver now presents larger capacitance to earlier stage.

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Wolf

## Optimal sizing

- Use a chain of inverters, each stage has transistors a larger than previous stage.

- Minimize total delay through driver chain:

$$-t_{tot} = n(C_{big}/C_g)^{1/n} t_{min}.$$

■ Optimal number of stages:

$$- n_{opt} = \ln(C_{big}/C_g).$$

■ Driver sizes are exponentially tapered with size ratio  $\alpha$ .

Modern VLSI Design 4e: Chapter 3

Copyright © 2008 Wayne Woli