## Chapter-4: Combinational Logic Networks

Modern VLSI Design 4e: Chapter 4

Copyright © 2008 Wayne Wolf

# Topics

The knowledge of logic gates, developed in the last chapter, will be used to analyze the delay and testability properties of combinational logic networks, including both the interconnect and the gates.

#### Placement & Routing

- Standard cell-based layout.

- Small gates, MUXs, Flipflops etc.

- Channel routing.

Modern VLSI Design 4e: Chapter 4

Copyright © 2008 Wayne Wolf

## Standard cell layout

- Layout made of small cells: gates, flip-flops, etc.

- Cells are hand-designed.

- Placement & Routing

Modern VLSI Design 4e: Chapter 4

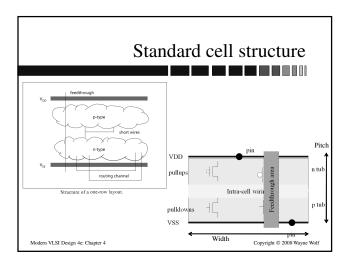

#### Standard cell design

- Pitch: height of cell.

- All cells have same pitch, may have different

- VDD, VSS connections are designed to run through cells.

- A feedthrough area may allow wires to be routed over the cell.

Modern VLSI Design 4e: Chapter 4 Copyright © 2008 Wayne Wolf

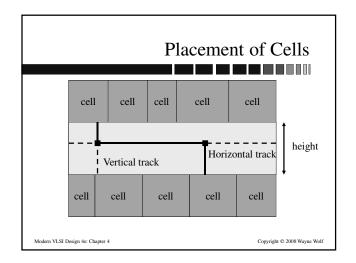

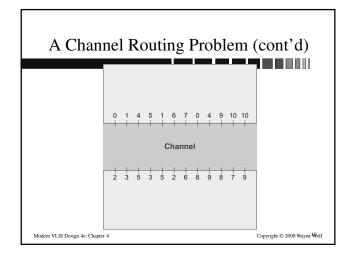

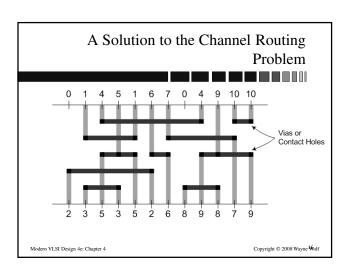

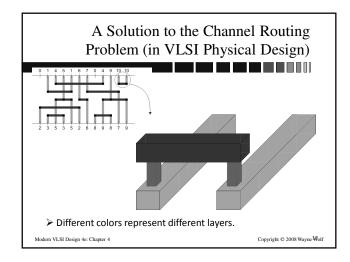

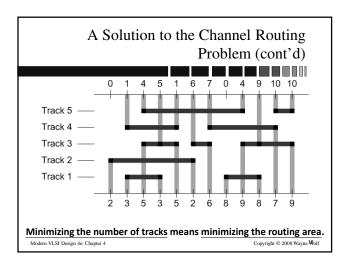

### Routing channels

- Tracks form a grid for routing.

- Spacing between tracks is center-to-center distance between wires.

- Track spacing depends on wire layer used.

- Different layers are (generally) used for horizontal and vertical wires.

- Horizontal and vertical can be routed relatively independently.

Modern VLSI Design 4e: Chapter 4

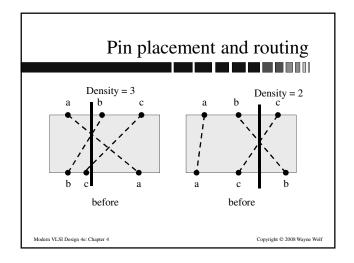

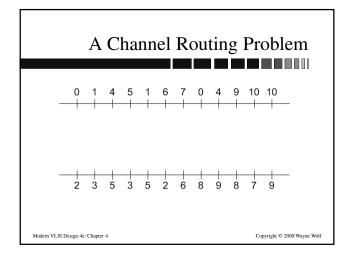

### Routing channel design

- Placement of cells determines placement of

- Pin placement determines difficulty of routing problem.

- Density: lower bound on number of horizontal tracks needed to route the channel.

- Maximum number of nets crossing from one end of channel to the other.

Modern VLSI Design 4e: Chapter 4

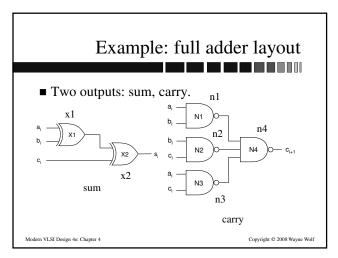

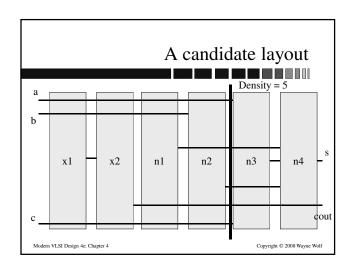

## Layout methodology

- Generate candidates, evaluate area and speed.

- Can improve candidate without starting from scratch.

- To generate a candidate:

- place gates in a row;

- draw wires between gates and primary inputs/outputs;

- measure channel density.

# Improvement strategies

- Swap pairs of gates.

- Doesn't help here.

- Exchange larger groups of cells.

- Swapping order of sum and carry groups doesn't help either.

- This seems to be the placement that gives the lowest channel density.

- Cell sizes are fixed, so channel height determines area.

Modern VLSI Design 4e: Chapter 4

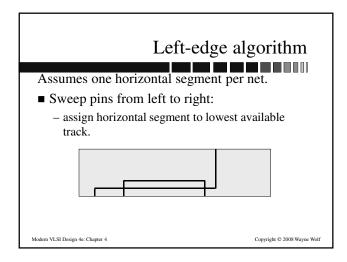

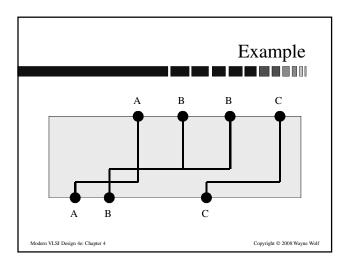

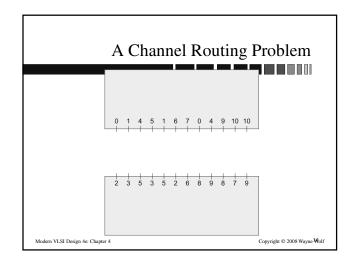

### The Left-Edge Algorithm

- Proposed by Hashimoto and Stevens in 1971

- Regarded as the first channel routing algorithm

- Can be used in solving Channel Routing Problems

- Originally used in PCB design

- Can be applied on VLSI physical design

- Requires building the Vertical Constraint Graph (VCG) for a channel routing problem

Modern VLSI Design 4e: Chapter 4