### Why we need design rules

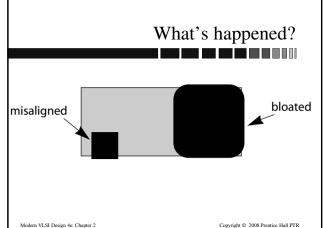

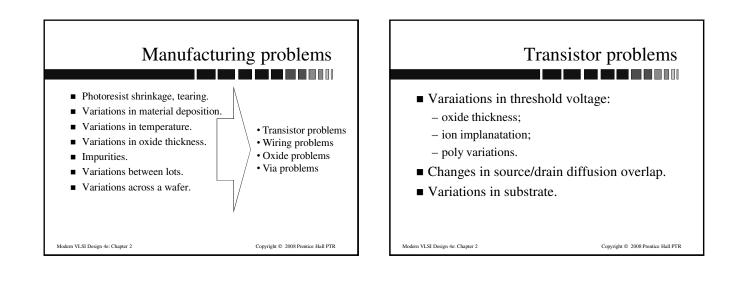

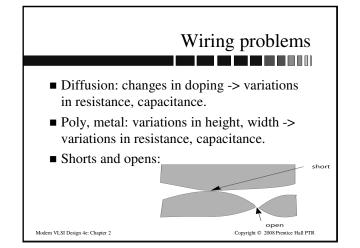

Design rules for a process are formulated to minimize the occurrence of common fabrication problems and bring the yield of correct chips to an acceptable level

- Manufacturing processes have inherent limitations in accuracy.

- Design rules specify geometry of masks which will provide reasonable yields.

- Design rules are determined by experience.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

# Design rules and yield

- Design rules are determined by manufacturing process characteristics.

- Design rules should provide adequate yield if followed.

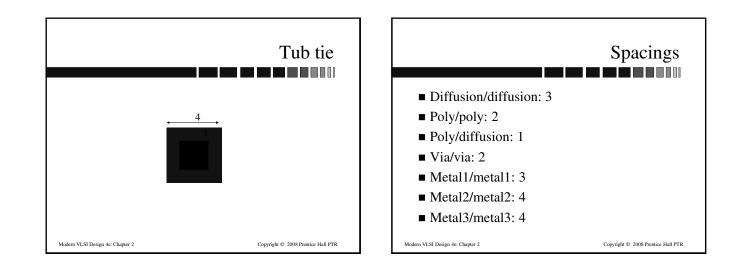

- Types of design rules:

- Spacing.

- Separation.

- Composition.

Modern VLSI Design 4e: Chapter 2

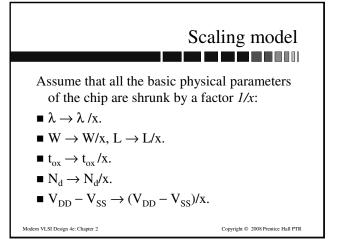

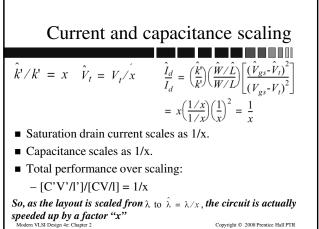

# Scaling theory

- In digital circuit design scaling is possible because the capacitive loads that must be driven by logic gates shrink faster than the currents supplied by the transistors.

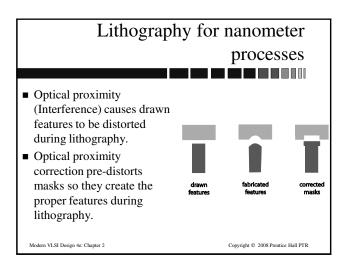

- Classical scaling theory runs into complications at nanometer features.

- Leakage.

Modern VLSI Design 4e: Chapter 2

- Smaller supply voltage.

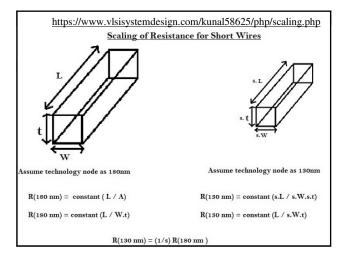

# Interconnect scaling

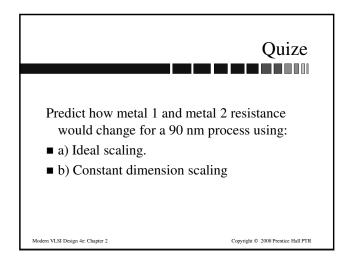

■ Two varieties of interconnect scaling:

- **Ideal scaling** reduces vertical and horizontal dimensions equally: *the resistance increases with scaling*.

- **Constant dimension** does not change wiring sizes: *resistance remains same*.

- Higher levels of interconnect are constant dimension---same as older technologies.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

#### MOSIS SCMOS design rules

- Designed to scale across a wide range of technologies.

- Designed to support multiple vendors.

- Designed for educational use.

- Ergo, fairly conservative.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

#### $\lambda$ and design rules

- $\blacksquare$   $\lambda$  is the size of a minimum feature.

- Specifying λ particularizes the scalable rules.

- Parasitics are generally not specified in  $\lambda$  units.

Modern VLSI Design 4e: Chapter 2

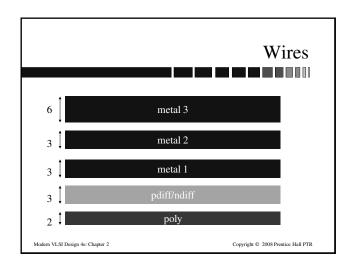

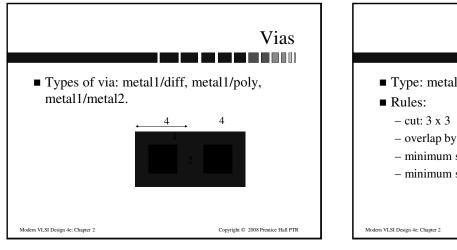

- Type: metal3/metal2.

- overlap by metal 2:1

- minimum spacing: 3

- minimum spacing to via1: 2

|                                 | SCMOS | SCMOS<br>submicron | SCMOS deep |

|---------------------------------|-------|--------------------|------------|

| Poly space                      | 2     | 3                  | 3          |

| Active extension<br>beyond poly | 3     | 3                  | 4          |

| Contact space                   | 2     | 3                  | 4          |

| Via width                       | 2     | 2                  | 3          |

| Metal 1 space                   | 2     | 3                  | 3          |

| Metal 2 space                   | 3     | 3                  | 4          |

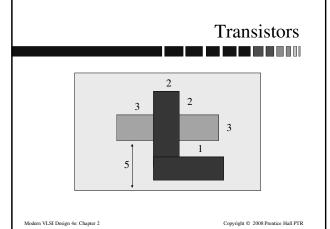

#### Assignment

• What SIZE is required to make the saturation drain current of a p-type transistor approximately equal to the saturation drain current of a minimum-width n-type transistor?

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

# 3-D integration

- 3-D technology stacks multiple levels of transistors and interconnect.

- Through-silicon-via (TSV) with die stacking uses special via to connect between separately fabricated chips.

- Multilayer buried structures build several layers of devices on a substrate.

Modern VLSI Design 4e: Chapter 2

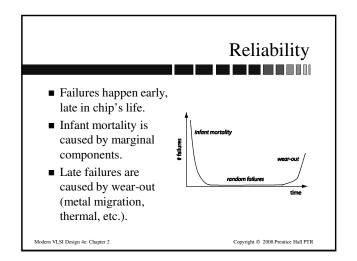

#### Mean-time-to-failure

- MTF for metal wires = time required for 50% of wires to fail.

- Depends on current density:

- proportional to  $j^{-n} e^{Q/kT}$

- j is current density

- n is constant between 1 and 3

- Q is diffusion activation energy

- Can determine lifetime from MTTF.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

#### Traditional sources of unreliability

- Diffusions and junctions: crystal defects, impurity precipitation, mask misalignment, surface contamination.

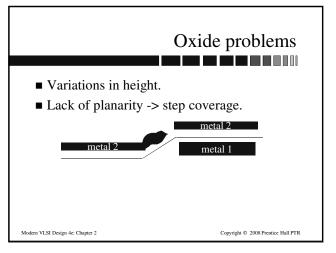

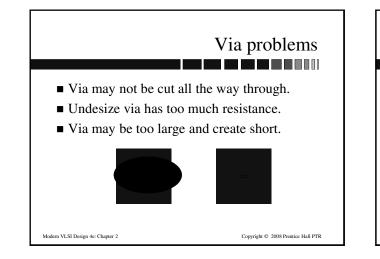

- Oxides: Mobile ions, pinholes, interface states, hot carriers, time-dependent dielectric breakdown.

- Metalization: scratches/voids, mechanical damage, non-ohmic contacts, step coverage.

Modern VLSI Design 4e: Chapter 2

# Electromigration and stress migration

- Degenerative failure for wires.

- Grains in metal have defects at grain surface that cause electromigration.

- Stress migration caused by mechanical stress.

- Can occur even with zero current.

Modern VLSI Design 4e: Chapter 2

Copyright © 2008 Prentice Hall PTR

# Soft errors

- Caused by alpha particles.

- Packages contain small amounts of uranium and thorium, which generate error-inducing radiation.

Modern VLSI Design 4e: Chapter 2